OpenAI запатентовала новую архитектуру ИИ-чипов

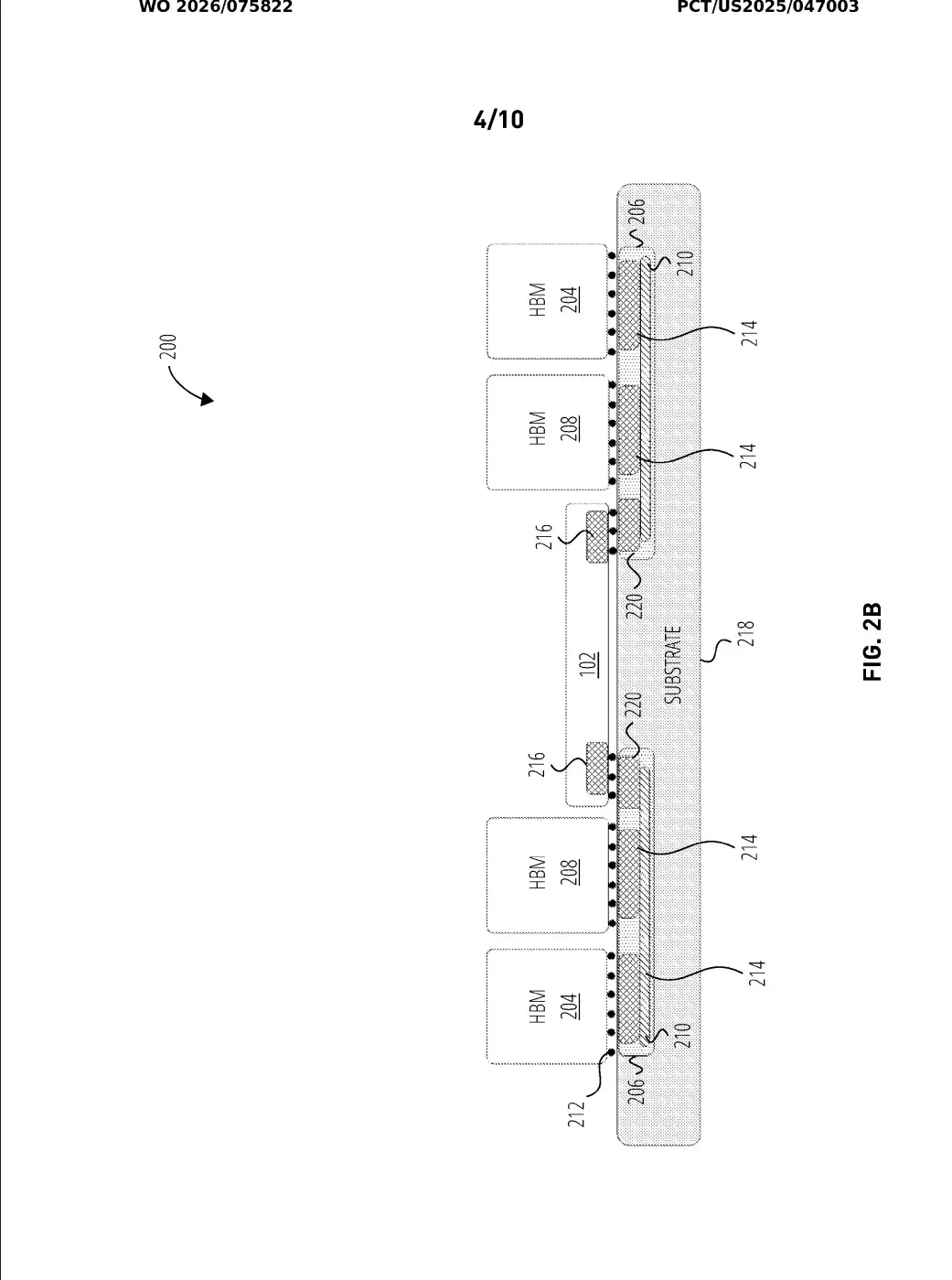

В опубликованном документе под названием «Несмежное соединение чиплетов HBM, ввода-вывода и вычислительных чиплетов через встроенные логические мосты» предлагается решение, позволяющее объединять вычислительные модули с беспрецедентно большим количеством стеков памяти HBM.

В современных системах интеграция HBM имеет строгие физические ограничения. Согласно действующим стандартам JEDEC, память должна располагаться вплотную к вычислительному кристаллу, так как длина металлических соединительных дорожек от контроллера PHY не может превышать 6 миллиметров. Из-за этого ограничения производители традиционно могут разместить вокруг одного процессора не более 4, 6 или 8 стеков памяти.

Для преодоления этого барьера OpenAI предлагает использовать встроенные логические мосты, которые позволяют увеличить дистанцию подключения с 6 до 16 миллиметров. Согласно патенту, эти мосты не только обеспечивают передачу данных на большее расстояние, но и могут брать на себя функции контроллера стека HBM или интерфейса PHY для связи между чиплетами внутри одной упаковки. Данный интерфейс полностью соответствует индустриальному стандарту UCIe.

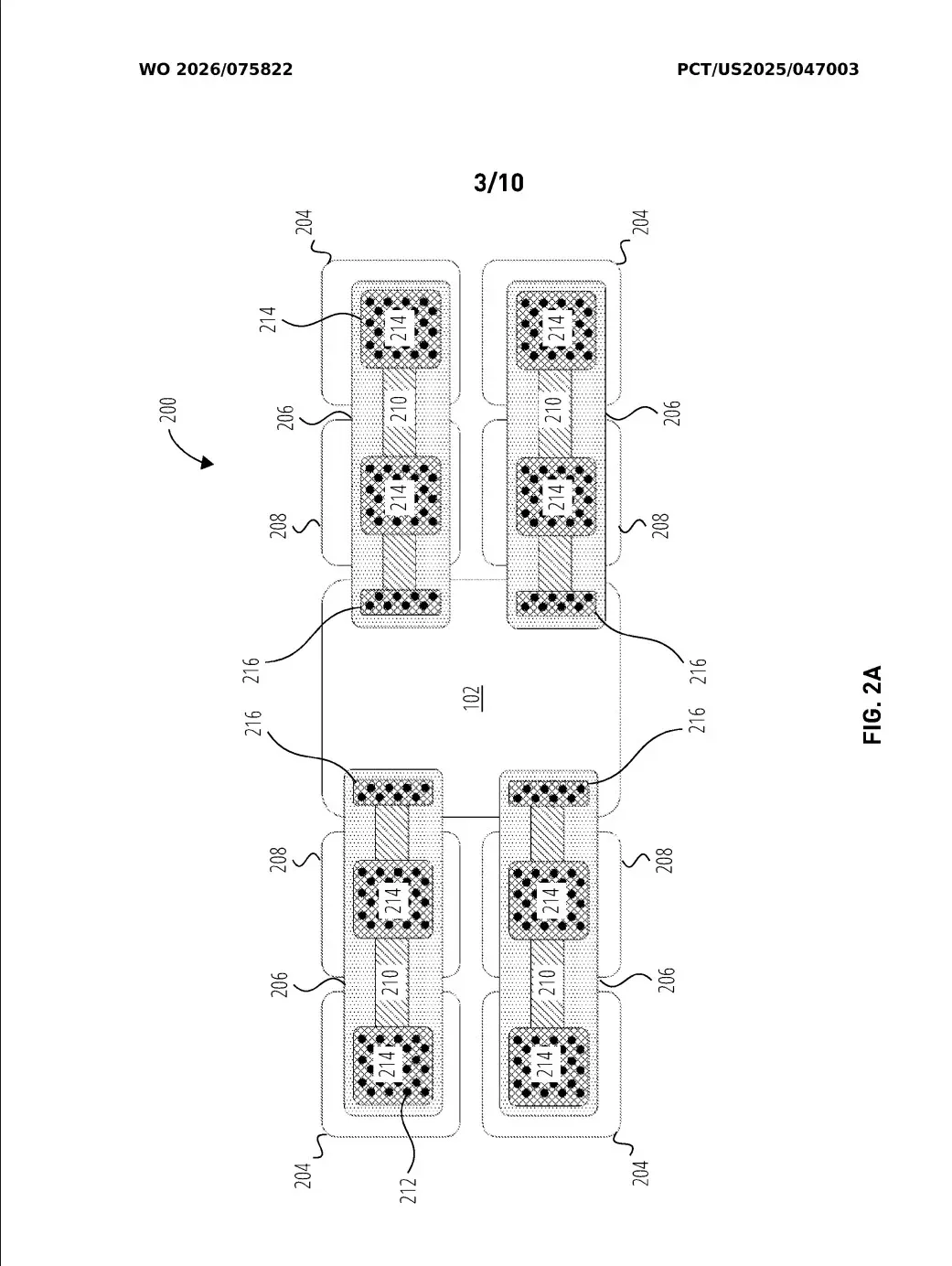

В качестве практического примера в документации приводится схема, в которой один вычислительный чиплет соединен сразу с 20 стеками памяти HBM.

Такое масштабирование многократно увеличивает объем и пропускную способность памяти, что является критически важным фактором для обучения и работы крупных языковых ИИ-моделей.

Технически описанный в патенте подход тесно перекликается с уже существующей на рынке технологией EMIB от Intel. Решение Intel для 2.5D-компоновки также использует миниатюрные кремниевые мосты, которые отличаются экономичностью, компактностью и позволяют создавать сложные высокопроизводительные чипы, выходящие за рамки стандартных ограничений размера фотошаблона.

Залогиньтесь, чтобы писать комментарии